Cache Aufgaben

Cache Miss

- Compulsory/Cold Miss

- Capacity Miss

- Conflict Miss

- Coherency Miss

- Nur bei Multiprozessor-Systemen mit Kohärenzprotokoll

- Unterscheidung zwischen False- und True-Sharing

- False-Sharing, falls nicht eigentliches Wort sondern anderes Wort in Cache-Block geändert wurde (See also: What’s false sharing and how to solve it)

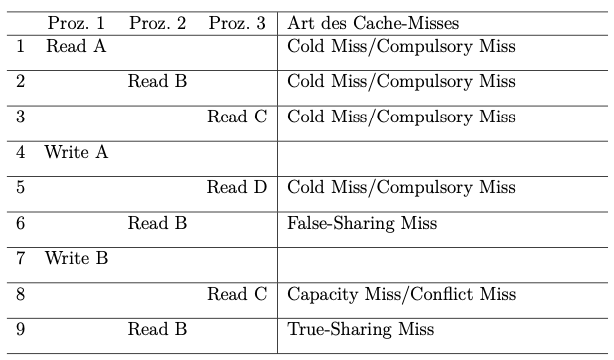

Bsp: Klausur SS17, Aufg. 3, (e)

- Multiprozessor mit gemeinsamen Speicher, der aus drei Prozessoreinheiten sowie Caches besteht.

- Jeder Cache bietet Platz für eine Cache-Zeile.

- Cache-Protokoll: MESI Protokoll

- Zugriff auf vier Variablen (A, B, C, D), wobei

- Variablen A,B und C dem selben Speicherblock angehören, also zusammen geladen werden

- D einem anderen Speicherblock angehör

- Beide Speicherblöcke werden auf die selbe Cache-Zeile abgebildet.

Klassifizieren Sie die auftretenden Cache Misses. Unterscheiden Sie dabei zwis- 4P chen True- und False-Sharing Misses.

False-Sharing Miss in Zeile 6:

Variablen A, B, C angehören dem selben Speicherblock. Prozessor 1 hat in Zeile 4 Variable A verändert.

Laut MESI Protokoll muss der selbe Speicherblock in andere Cache des anderen Prozessors invalidiert werden. $\Rightarrow$ Cache Miss

Da NICHT eigentliches Wort B, sondern Variable A, also das andere Wort, in Cache-Block geändert wird, ist dieses Cache Miss daher ein False-Sharing Miss.

True-Sharing Miss in Zeile 9:

Variable B ist in Zeile 7 geändert. D.h. das eigentliche (dasselbe) Wort wird geändert

$\Rightarrow$ True-Sharing

Mehrstufiger Cache-Architektur

Achtung:

Wie der Zugriff auf die nächste Ebene stattfindet (sequentiell oder parallel)?

Beim sequntiellen Zugriffe auf die nächste Ebene $$ t_{a}=\underbrace{r_{H 1} * t_{L 1}}_{\text{Hit L1}} + \underbrace{r_{M1} *(\underbrace{r_{H2} *\left(t_{L1}+t_{L2}\right)}_{\text{Hit L2}}+\underbrace{r_{M2} *(t_{L1}+t_{L2}+t_{Mem})}_{\text{Miss L2}})}_{\text{Miss L1}} $$

- Bsp: SS18, Aufg.3, (b)

Beim parallelen Zugriffe auf die nächste Ebene

- Die Zugriffszeit höherer Ebene beim Miss kann in Zugriffszeit niedrigerer Ebene verstecken.

$$ t_{a}=\underbrace{r_{H 1} * t_{L 1}}_{\text{Hit L1}} + \underbrace{r_{M1} *(\underbrace{r_{H2} *t_{L2}}_{\text{Hit L2}}+\underbrace{r_{M2} *t_{Mem}}_{\text{Miss L2}})}_{\text{Miss L1}} $$

- Bsp: WS1819, Aufg.3, (c)

Cache Kohärenzprotokolle

- Verzeichnis-/Tabellen-basierte Protokolle (directory-based protocols)

- Snooping-Protokolle (Bus-Schnüffeln)

- Write-Invalid Protokoll

- MSI

- MESI

- MOESI

- Write-Update Protokoll

- Write-Invalid Protokoll