VLIW

VLIW = Very Long Instruction Word

TL;DR

- Befehlswort aus mehreren einzelnen Befehlen zusammengesetzt

- Parallelität explizit vom Compiler angegeben

- Statisches Konzept

Grundprinzip

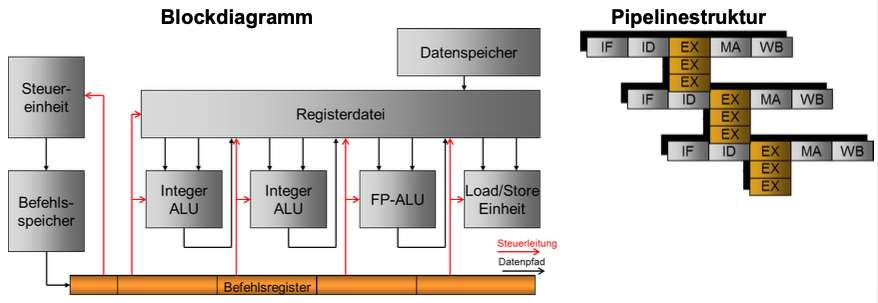

Breites Befehlsformat, das in mehrere Felder aufgeteilt ist, aus denen die Funktionseinheiten gesteuert werden

Eine VLIW-Architektur mit $n$ voneinander unabhängigen Funktionseinheiten kann bis zu $n$ Operationen gleichzeitig ausführen

Operationen: RISC-ähnliche Befehlssatzarchitekturr

Automatisch parallelisierender Compiler: Steuerung der parallelen Abarbeitung zur Übersetzungszeit

Statische Steuerung der parallelen Abarbeitung

Aufgaben des Compilers

Frontend:

- Lexikalische, syntaktische und semantische Analyse

Code-Generierung / Parallelisierung

- Kontrollflussanalyse

- Datenflussanalyse

- Datenabhängigkeitsanalyse

Schleifenparallelisierung

- Loop Unrolling

- Software-Pipelining

Scheduling

- Packen der voneinander unabhängigen Befehle in breite Befehlswörter

Beispiel

Siehe: Ub5-VLIW Prozessoren

Very long instruction word (VLIW) refers to instruction set architectures designed to exploit instruction level parallelism (ILP). Whereas conventional central processing units (CPU, processor) mostly allow programs to specify instructions to execute in sequence only, a VLIW processor allows programs to explicitly specify instructions to execute in parallel. This design is intended to allow higher performance without the complexity inherent in some other designs.

A processor that executes every instruction one after the other (i.e., a non-pipelined scalar architecture) may use processor resources inefficiently, yielding potential poor performance. The performance can be improved by executing different substeps of sequential instructions simultaneously (termed pipelining), or even executing multiple instructions entirely simultaneously as in superscalar architectures. Further improvement can be achieved by executing instructions in an order different from that in which they occur in a program, termed out-of-order execution.

These three methods all raise hardware complexity. Before executing any operations in parallel, the processor must verify that the instructions have no interdependencies. For example, if a first instruction’s result is used as a second instruction’s input, then they cannot execute at the same time and the second instruction cannot execute before the first. Modern out-of-order processors have increased the hardware resources which schedule instructions and determine interdependencies.

In contrast, VLIW executes operations in parallel, based on a fixed schedule, determined when programs are compiled. Since determining the order of execution of operations (including which operations can execute simultaneously) is handled by the compiler, the processor does not need the scheduling hardware that the three methods described above require. Thus, VLIW CPUs offer more computing with less hardware complexity (but greater compiler complexity) than do most superscalar CPUs.