Ub2-VHDL Portmapping Example

Source: Port mapping example

Task

Given two modules as follows:

library IEEE;

use IEEE.std_logic_1164.all;

entity module_a is

port (

clk: in std_logic;

input_a: in std_logic;

output_a: out std_logic

);

end module_a

architecture behav of module_a is

begin

output_a <= input_a;

end behav;

library IEEE;

use IEEE.std_logic_1164.all;

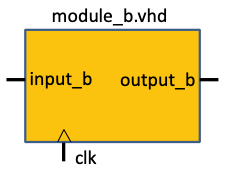

entity module_b is

port (

clk: in std_logic;

input_b: in std_logic;

output_b: out std_logic

);

end module_b

architecture behav of module_b is

begin

output_b <= input_b;

end behav;

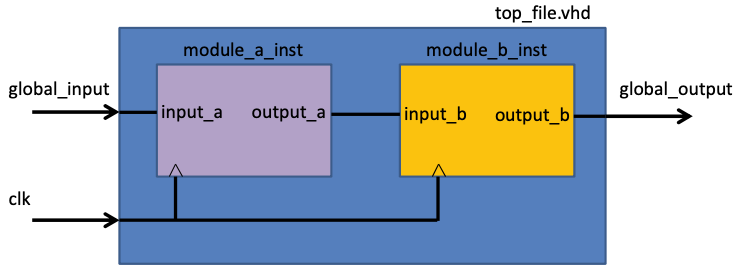

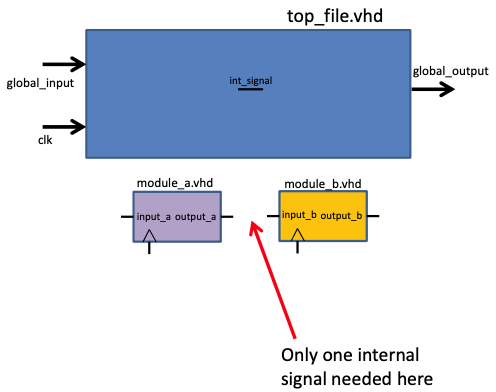

Portmap them as follows:

Step by step

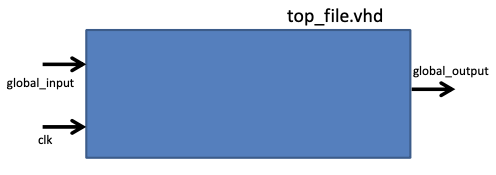

- Create empty top_file shell (only define ports)

library IEEE;

use IEEE.std_logic_1164.all;

-- Step 1

entity top_file is

port (

clk: in std_logic;

global_input: in std_logic;

global_output: out std_logic;

);

end top_file;

architecture behav of top_file is

begin

end behav;

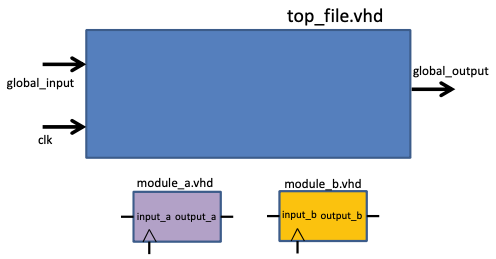

2. Declare the modules

Note: no instantiation of the modules exists yet!

library IEEE;

use IEEE.std_logic_1164.all;

-- Step 1

entity top_file is

port (

clk: in std_logic;

global_input: in std_logic;

global_output: out std_logic;

);

end top_file;

architecture behav of top_file is

-- Step 2

-- (Same as entity in vhd file, only named component)

component module_a

port (

clk: in std_logic;

input_a: in std_logic;

output_a: out std_logic

);

end component;

component module_b is

port (

clk: in std_logic;

input_b: in std_logic;

output_b: out std_logic

);

end component

begin

end behav;

3. Define needed internal signals

library IEEE;

use IEEE.std_logic_1164.all;

-- Step 1

entity top_file is

port (

clk: in std_logic;

global_input: in std_logic;

global_output: out std_logic;

);

end top_file;

architecture behav of top_file is

-- Step 2

-- (Same as entity in vhd file, only named component)

component module_a

port (

clk: in std_logic;

input_a: in std_logic;

output_a: out std_logic

);

end component;

component module_b is

port (

clk: in std_logic;

input_b: in std_logic;

output_b: out std_logic

);

end component

-- Step 3

signal int_signal : std_logic;

begin

end behav;

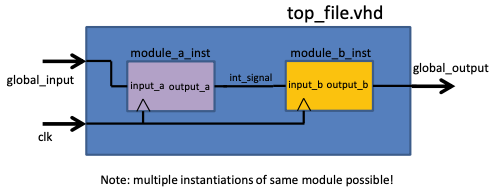

4. Instantiate and portmap to connect the modules

library IEEE;

use IEEE.std_logic_1164.all;

-- Step 1

entity top_file is

port (

clk: in std_logic;

global_input: in std_logic;

global_output: out std_logic;

);

end top_file;

architecture behav of top_file is

-- Step 2

-- (Same as entity in vhd file, only named component)

component module_a

port (

clk: in std_logic;

input_a: in std_logic;

output_a: out std_logic

);

end component;

component module_b is

port (

clk: in std_logic;

input_b: in std_logic;

output_b: out std_logic

);

end component

-- Step 3

signal int_signal : std_logic;

begin

-- Step 4

module_a_inst: module_a

port map (

input_a => global_input;

clk => clk;

output_a => int_signal

);

module_b_inst: module_n

port map (

input_b => int_signal;

clk => clk;

output_b => global_output

);

end behav;