Ub5-VLIW Prozessoren

Überblick

Befehlswort aus mehreren einzelnen Befehlen zusammengesetzt

Parallelität explizit vom Compiler angegeben

Statisches Konzept

”Platzhalter“ in Befehlswort für jede vorhandene Ausführungseinheit

Sinnvoll bei Spezialanwendungen: DSP, Graphik, Netzwerk

Moderne Varianten: EPIC (Intel Itanium), Transmeta Crusoe

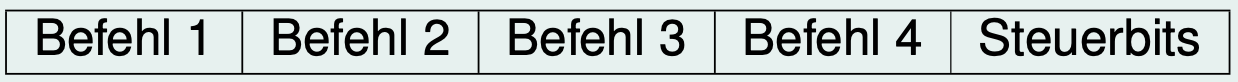

Befehlformat

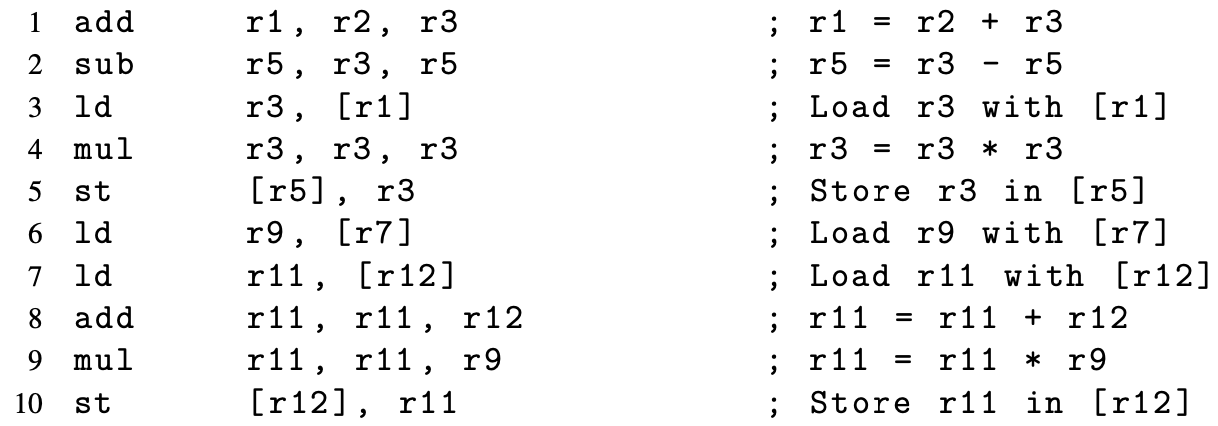

Aufgabe

Der folgende Assembler-Code soll auf einem VLIW-Prozessor mit drei parallelen Ausfüh- rungseinheiten ausgeführt werden. Geben Sie hierfür eine möglichst effiziente Befehlsvertei- lung an. Die Befehle können beliebig umsortiert werden, so lange die Korrektheit der Anwen- dung gewährleistet ist.

Abhängigkeit:

Befehl 3 is abhängig von Befehl 2

Befehl 4 und 5 sind abhängig von Befehl 3

Befehl 8 und 9, 10 sind abhängig von Befehl 7

Befehl 9 is abhängig von Befehl 6

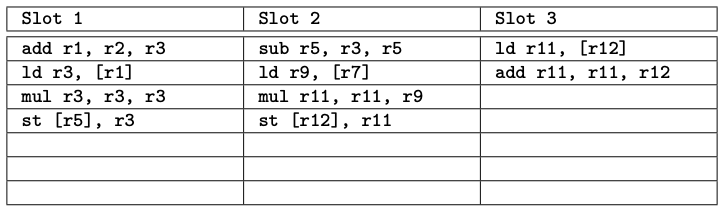

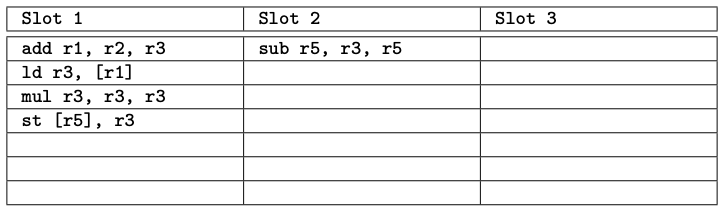

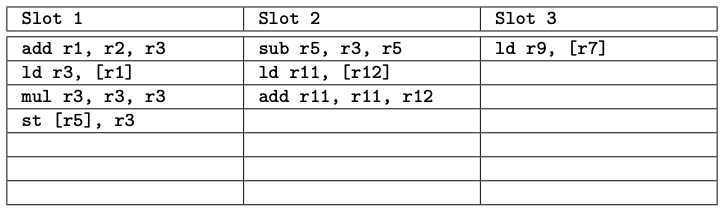

Teilaufgabe (a)

Nehmen Sie an, dass der Prozessor über drei Ausführungseinheiten verfügt, die jeweils alle Befehle ausführen können.

Zuordnung Befehl 3, 4, 5: Abhängigkeiten beachten

Abhängigkeit

$\Rightarrow$ Befehl muss in nächste VLIW (also nächste Zeile)

Zuordnung Befehl 6, 7, 8

Zuordnung Befehl 8

- Befehle 9 und 10 auch von Befehl 7 abhängig

- führt zu langer Befehlsfolge und einem nötigen 5. Befehl 🤪

$\Rightarrow$ Optimierung notwendig! 💪

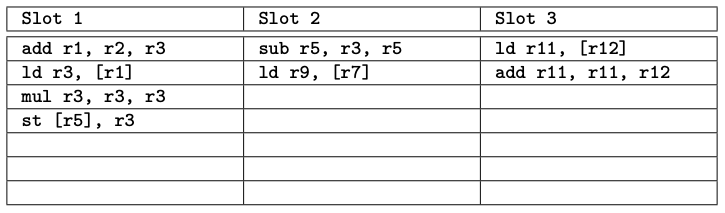

Da Befehl 6 (ld r9, [r7]) und Befehl 7 (ld r11, [r12]) nicht abhängig sind, könne die beide Befehlen vertauscht werden. Und wir haben die Neuordnung von Befehl 8.

Zuordnung restlicher Befehle